### OVERVIEW

The SM5828B is a variable-length 8-bit shift register fabricated using NPC's original molybdenum-gate CMOS technology. The external input pins of the IC allow 1 to 128-step shift register settings. The shift clock with the maximum frequency of 20 MHz ensures high-speed operation. As static registers are used, data is retained even when the shift clock is stopped.

### ■ FEATURES

- 1 to 128-step settings

- 8-bit (1-byte) parallel input/output

- · Static registers

- Selection between circulation and noncirculation

- Maximum operating clock frequency 20 MHz

- Supply voltage 5 V ±0.5 V

- Input/output TTL compatible

- 28-pin DIP (plastic, ceramic)

- Molybdenum-gate CMOS construction

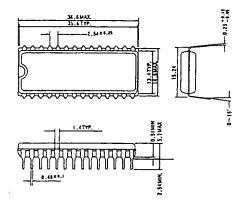

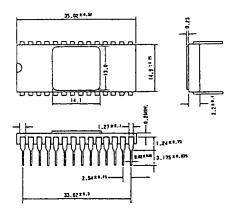

# ■ PACKAGE DIMENSIONS (Unit: mm)

• Plastic (SM5828BP)

### PACKAGE TYPES

| Туре     | Package            |

|----------|--------------------|

| SM5828BP | 28-pin plastic DIP |

| SM5828BC | 28-pin ceramic DIP |

### ■ PINOUT TOP VIEW

• Ceramic (SM5828BC)

\* The SM5828BC guarantees high reliability.

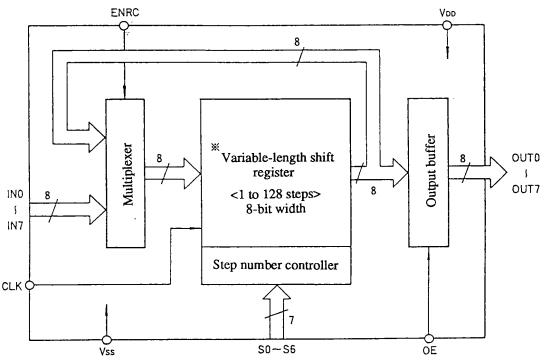

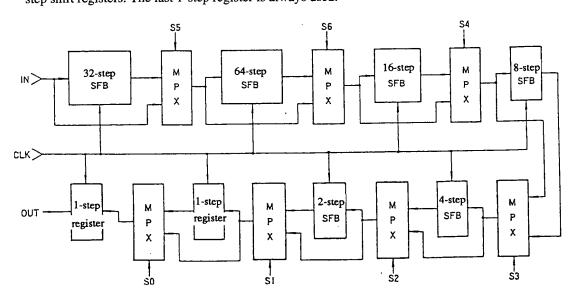

## ■ BLOCK DIAGRAM

\* Internal configuration of the variable-length shift register

The figure below shows the configuration of the variable-length shift register. According to the setting of S0 to S6, the multiplexer selects the output of each shift register block, realizing 1 to 128-step shift registers. The last 1-step register is always used.

MPX: Multiplexer

SFB: Shift register block

## ■ PIN DESCRIPTION

| No | Name            | Description                             |  |  |  |

|----|-----------------|-----------------------------------------|--|--|--|

| 1  | INO:            | Data input (0)                          |  |  |  |

| 2  | IN1             | Data input (1)                          |  |  |  |

| 3  | IN2             | Data input (2)                          |  |  |  |

| 4  | IN3             | Data input (2)  Data input (3)          |  |  |  |

| 5  | IN4             | Data input (4)                          |  |  |  |

| 6  | IN5             | Data input (5)                          |  |  |  |

| 7  | IN6             | Data input (6)                          |  |  |  |

| 8  | IN7             | Data input (7)                          |  |  |  |

| 9  | S6              | Data length select (6)                  |  |  |  |

| 10 | S5              | Data length select (5)                  |  |  |  |

| 11 | S4              | Data length select (4)                  |  |  |  |

| 12 | S3              | Data length select (3)                  |  |  |  |

| 13 | CLK             | Clock input                             |  |  |  |

| 14 | Vss             | Ground                                  |  |  |  |

| 15 | S2              | Register length select (2)              |  |  |  |

| 16 | S1              | Register length select (1)              |  |  |  |

| 17 | S0              | Register length select (0)              |  |  |  |

| 18 | OUT7            | Data output (7)                         |  |  |  |

| 19 | OUT6            | Data output (6)                         |  |  |  |

| 20 | OUT5            | Data output (5)                         |  |  |  |

| 21 | OUT4            | Data output (4)                         |  |  |  |

| 22 | OUT3            | Data output (3)                         |  |  |  |

| 23 | OUT2            | Data output (2)                         |  |  |  |

| 24 | OUT1            | Data output (1)                         |  |  |  |

| 25 | OUT0            | Data output (0)                         |  |  |  |

| 26 | OE              | Output enable                           |  |  |  |

| 27 | ENRC            | Circulation and non-circulation control |  |  |  |

| 28 | V <sub>DD</sub> | Power supply $(5 \pm 0.5 \text{ V})$    |  |  |  |

Note All input pins have pull-up resistors. All output pins are in tristate.

# ■ ABSOLUTE MAXIMUM RATINGS

| Parameter             | Symbol          | Rating                        | Unit |

|-----------------------|-----------------|-------------------------------|------|

| Supply voltage        | V <sub>DD</sub> | -0.3 to 7.0                   | V    |

| Input voltage         | Vin             | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage temperature   | Тѕтс            | -40 to 125                    | °C   |

| Power dissipation     | Pw              | 750                           | mW   |

| Soldering temperature | Tsld            | 255                           | °C   |

| Soldering time        | tsld            | 10                            | Sec  |

# ■ RECOMMENDED OPERATING CONDITIONS

(Vss = 0V)

| Parameter                             | Symbol   | Condition  | Unit |

|---------------------------------------|----------|------------|------|

| Supply voltage                        | $V_{DD}$ | 4.5 to 5.5 |      |

| Operating<br>temperature<br>(SM5828P) | Toprp    | –20 to 70  | °C   |

| Operating<br>temperature<br>(SM5828C) | Toprc    | -30 to 85  | °C   |

### ■ DC CHARACTERISTICS

SM5828BP ... Ta = -20 to 70 °C, VDD = 4.5 to 5.5 V, Vss = 0 V SM5828BC... Ta = -30 to 85 °C, VDD = 4.5 to 5.5 V, Vss = 0 V unless otherwise noted.)

| Paramete                             | Pin | Symbol | Condition                 | Rating |      |     | Unit | Remarks       |

|--------------------------------------|-----|--------|---------------------------|--------|------|-----|------|---------------|

| Taramete                             | ķm  | Symbol | Condition                 | MIN    | TYP  | MAX |      | Remarks       |

| Current consumption at standby       | VDD | Isт    | V <sub>DD</sub> = 5.5V    |        | 0.01 | 100 | μΑ   |               |

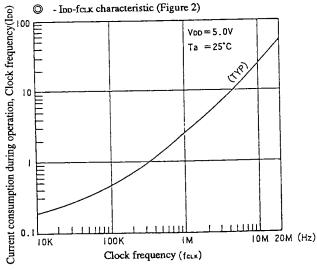

| Current consumption during operation | Vdd | IDD    | Note                      |        |      | 100 | mA   | See Figure 2. |

| Input voltage                        | *1  | Vih    |                           | 2.4    |      |     | V    |               |

| _                                    |     | VIL    |                           |        |      | 0.5 |      |               |

| Output voltage                       | *2  | Vон    | $I_{OH} = -0.4 \text{mA}$ | 2.5    |      |     | V    |               |

| _                                    |     | Vol    | IoL= 1.6mA                |        |      | 0.4 |      |               |

| Input current                        | *1  | In     | $V_{IN} = 0V$             |        | 7    | 20  | μA   |               |

| Input leak current                   | *1  | ILH    | $V_{IN} = V_{DD}$         |        |      | 1   | μΑ   |               |

| Output Hi-Z current                  | *2  | Izн    | Vout = Vdd                |        |      | 5   | μΑ   |               |

|                                      |     | Izı    | Vout = 0V                 |        |      | 5   |      |               |

(Pin type)

| * 1 | ENRC, INO to IN7, SO to S6, CLK, OE |

|-----|-------------------------------------|

| * 2 | OUT1 to OUT7                        |

Note) Clock frequency fcL $\kappa$  = 20 MHz, OE pin = 0 V Clock input voltage V<sub>IH</sub> = 2.4 V, V<sub>IL</sub> = 0.5 V

## ■ AC CHARACTERISTICS

(VDD = 4.5 to 5.5 V, Vss = 0 V unless otherwise noted)

| Paramete             | Pin Symbo |                 | Condition                                         |          | BC type(-20 to 85°C) |          | BC type (-30 to 70°C) |     |     | Unit | Remarks  |  |    |  |  |

|----------------------|-----------|-----------------|---------------------------------------------------|----------|----------------------|----------|-----------------------|-----|-----|------|----------|--|----|--|--|

|                      |           |                 |                                                   | MIN      | TYP                  | MAX      | MIN                   | ГҮР | MAX |      |          |  |    |  |  |

| Clock frequency      | CLK       | fclk            | $V_{IH} = 2.4V$ , $V_{IL} = 0.5V$                 |          |                      | 20       |                       |     | 20  | MHz  |          |  |    |  |  |

| Clock rise time      | CLK       | tcr             |                                                   |          |                      | 100      |                       |     | 100 | nsec |          |  |    |  |  |

| Clock fall time      | CLK       | tcf             |                                                   |          |                      | 100      |                       |     | 100 | nsec |          |  |    |  |  |

| Clock pulse width    | CLK       | twн             |                                                   | 20       |                      |          | 20                    |     |     | nsec |          |  |    |  |  |

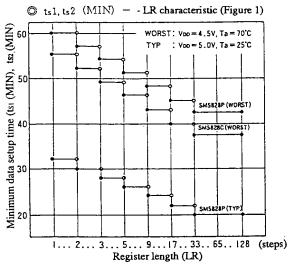

|                      | IN0 to 7  | ts1             | Register length: LR<br>= 1 to 16 steps Figure 1   | 60       |                      |          | 55                    |     |     | nsec | Figure 1 |  |    |  |  |

| Input setup time     | ENRC      | ts2             | Register length: LR<br>= 17 to 128 steps Figure 1 | 45       |                      |          | 40                    |     |     | nsec | Figure 1 |  |    |  |  |

|                      | SO to 6   | ts3             |                                                   | 80       |                      |          | 80                    |     |     | nsec |          |  |    |  |  |

|                      | INO to 7  |                 |                                                   | 0        |                      |          | 0                     |     |     | nsec |          |  |    |  |  |

| Input hold time      | ENRC      | IRC thi         |                                                   | 0        |                      | <u> </u> |                       |     |     | nscc |          |  |    |  |  |

| input note that      | S0 to 6   | t <sub>H2</sub> |                                                   | 10       |                      |          | 10                    |     |     | nsec |          |  |    |  |  |

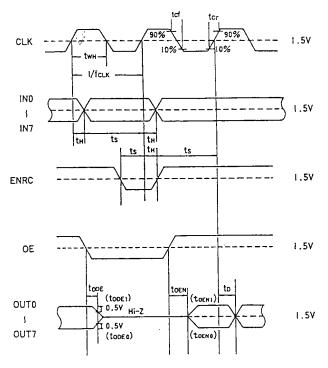

| Output enable delay  | OUT       |                 | Load condition 1                                  |          |                      |          |                       |     |     |      | 77. 0    |  |    |  |  |

| time                 | 0 to 7    | toen            | (Note 1)                                          |          |                      | 40       |                       |     | 35  | nsec | Figure 3 |  |    |  |  |

| Output disable delay | OUT       | tope            | Load condition 1                                  |          |                      |          |                       |     |     |      | Eigura 2 |  |    |  |  |

| time                 | 0 to 7    | LODE            | (Note 1)                                          | <u> </u> | <u></u>              | 40       |                       |     | 35  | nsec | Figure 3 |  |    |  |  |

| Output data delay    | OUT       | tn              | Load condition 2                                  |          |                      | 45       |                       |     | 40  | nsec | Figure 3 |  |    |  |  |

| time                 | 0 to 7    | t <sub>D</sub>  | (Note 2)                                          |          | 43                   |          | 43                    |     | 45  |      | 40       |  | 40 |  |  |

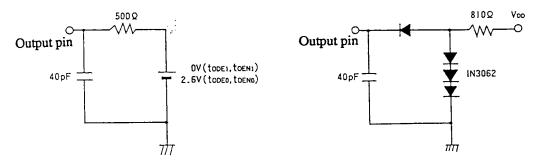

(Note 1) Load condition 1

(Note 2) Load condition 2

# ■ REGISTER STEP SETTING

Set the number of register steps by using the register length select pins S0 to S6.

| L=64•(S6)+32•( | 95)±16•(S | (4)+8(\$3)+4         | •(S2)+2•(S             | 1)+(S0)+1 |

|----------------|-----------|----------------------|------------------------|-----------|

| L=04*(30)+32*( | 99)+10•(9 | 14)+0( <i>33)+</i> 4 | *(32) <del>*</del> *(3 | 1/7(30/71 |

| Step | <b>S</b> 6 | S5 | S4 | S3 | S2 | S2 | S0 |

|------|------------|----|----|----|----|----|----|

| 128  | 1          | 1  | 1  | 1  | 1  | 1  | 1  |

| 127  | 1          | 1  | 1  | 1  | 1  | 1  | 0  |

| 126  | 1          | 1  | 1  | 1  | 1  | 0  | 1  |

| 125  | 1          | 1  | 1  | 1  | 1  | 0  | 0  |

|      |            |    |    | •  |    |    |    |

| ·    |            |    |    | •  |    |    |    |

| .    |            |    |    |    |    |    |    |

| 66   | 1          | 1  | 0  | 0  | 0  | 0  | 1  |

| 65   | 1          | 1  | 0  | 0  | 0  | 0  | 0  |

|      |            |    |    | •  |    |    |    |

|      |            |    |    | •  |    |    |    |

|      |            |    |    | •  |    |    |    |

| 3    | 0          | 0  | 0  | 0  | 0  | 1  | 0  |

| 2    | 0          | 0  | 0  | 0  | 0  | 0  | 1  |

| 1    | 0          | 0  | 0  | 0  | 0  | 0  | 0  |

|      | <u> </u>   |    |    |    |    |    |    |

Note)

1. 1 ... High or Open,

0 .... Low

2. S0 to S6 pins have internal pull-up resistors.

# ■ INPUT/OUTPUT CONTROL

|      | Input    |    | Shift register | Output       |

|------|----------|----|----------------|--------------|

| ENRC | CLK      | OE | (internal)     | OUT0 to OUT7 |

| X    | X        | 0  | _              | Hi–Z         |

| X    | X        | 1  | _              | ENABLE       |

| 1    | <i>f</i> | X  | Circulation    | _            |

| 0    | <i></i>  | X  | No circulation |              |

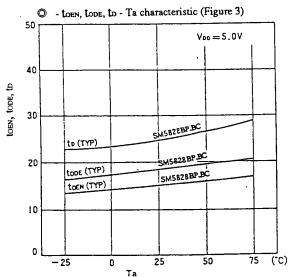

## **■ TYPICAL CHARACTERISTICS**

## TIMING CHART

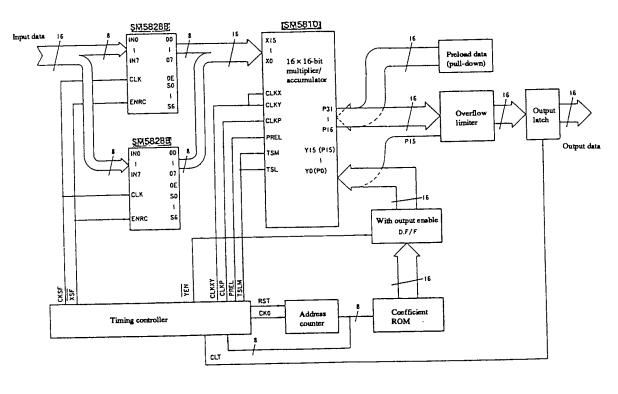

■ TYPICAL APPLICATION (Block diagram of a 16-bit FIR digital filter using the SM5828B)