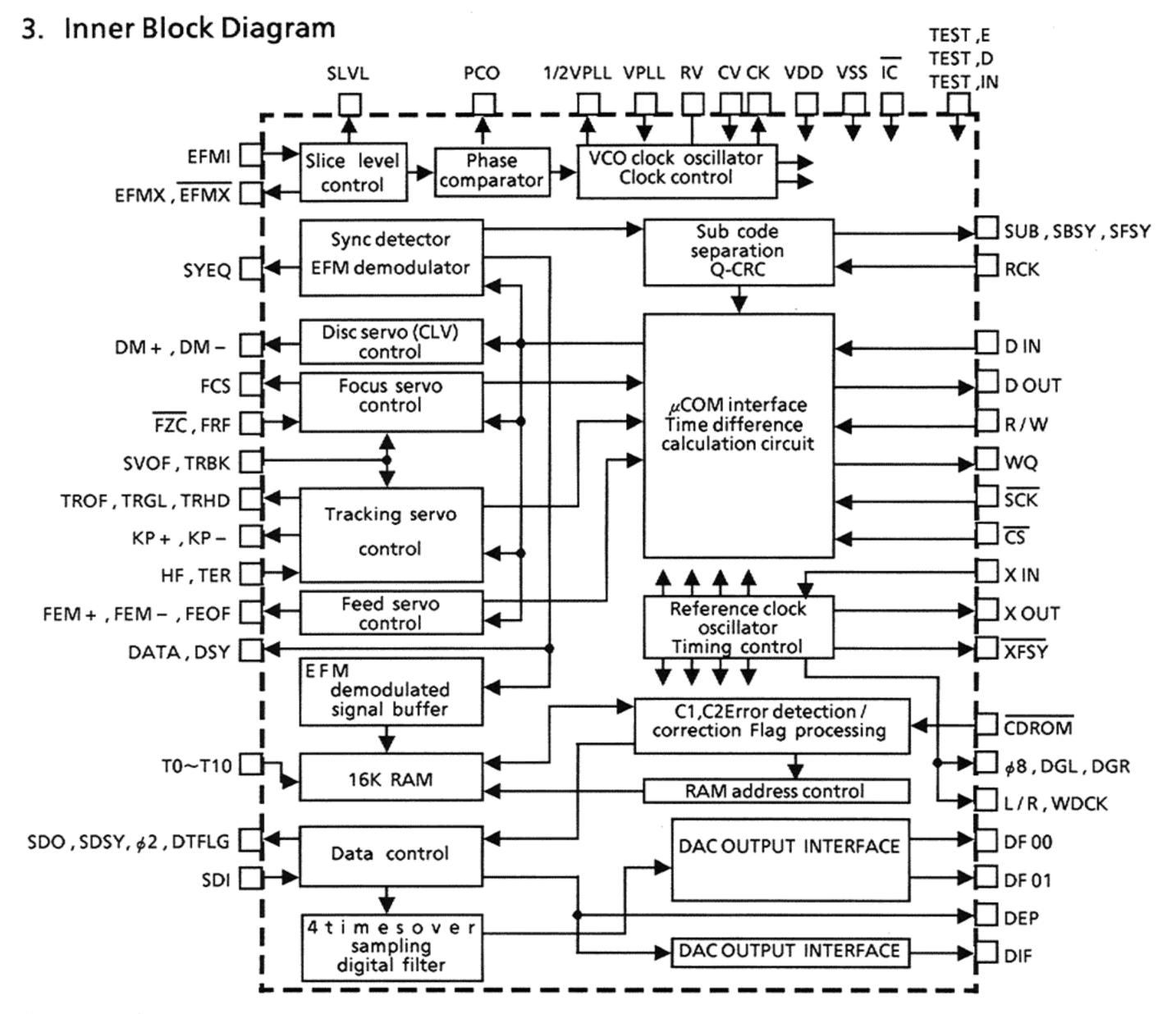

## Description of Major LSIs

## YM7121B(IC401)

## 1. Outline

YM7121 is a C-MOS LSI for signal processing and servo control (SVC) in a CD player. It is used for the demodulation of the EFM signal from the laser pick up, detection / correction of the error signal, signal processing in digital filtering, etc. and for various servo controls (focusing, disc, tracking and feed servos).

And it contains digital interface which output the audio digital signals in S-RAM and CD-player. This digital interface matches EIAJ standards.

## 4. Terminal Function

| Pin No.                                                                    | Symbol                                                                                         | 1/0          | Function and Operation                                                                                                                                                                                                   |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                          | cv                                                                                             | 1            | Adequate time constant is added to this terminal and input the PCO output. This makes the structure of clock reproduce circuit by inner VCO circuit.                                                                     |

| 2                                                                          | RV                                                                                             | -            | RV terminal is standard voltage terminal of inner VCO. And capacity for stabilizing is added to this terminal.                                                                                                           |

| 3<br>32<br>72                                                              | VDD                                                                                            | 1            | These are +5V power supply terminals.                                                                                                                                                                                    |

| 4<br>5<br>70                                                               | TEST. IN<br>TEST. E<br>TEST. D                                                                 |              | These terminals are for test.                                                                                                                                                                                            |

| 6                                                                          | SYEQ                                                                                           | 0            | This is the check output terminal, it becomes high when flame synchronizing signal detected from EFM pattern coincides frame synchronizing signal from internal counter.                                                 |

| 7                                                                          | DSY                                                                                            | 0            | DSY is synchronizing signal which becomes high when first signal of data output comes in. This terminal is the check terminal.                                                                                           |

| 8                                                                          | DATA                                                                                           | 0            | This terminal is for checks. The DATA is a serial signal of CK bit rate and it contains 8 bit EFM demodulation signal and 5 bit data control signal in 17 bit.                                                           |

| 9                                                                          | CK                                                                                             | 0            | CK has 4.3218 MHz clock.                                                                                                                                                                                                 |

| 10~19                                                                      | T0~T9                                                                                          | ١            | This terminal is internal RAM test terminal, and connected GND.                                                                                                                                                          |

| 22                                                                         | DEP                                                                                            | 0            | De-emphasis is necessary when this terminal is high.                                                                                                                                                                     |

| 23                                                                         | DIF                                                                                            | 0            | DIF is digital audio interface format output matched EIAJ standards.                                                                                                                                                     |

| 24                                                                         | SDO                                                                                            | 0            | SDO is a serial signal output of \$2 bit rate. (The MSB puts in at first.)                                                                                                                                               |

| 25                                                                         | SDI                                                                                            | ı            | SDI is the input terminal of 4 times over sampling digital filter. It is usually connected with SDO.                                                                                                                     |

| 26                                                                         | SDSY                                                                                           | 0            | This terminal changes the Lch/Rch by LSB of the SDO.                                                                                                                                                                     |

| 27                                                                         | DTFLG                                                                                          | 0            | Not used.                                                                                                                                                                                                                |

| 28                                                                         | φ2                                                                                             | 0            | φ2 is 2.1168 MHz crystal clock.                                                                                                                                                                                          |

| 29, 52, 77                                                                 | VSS                                                                                            | -            | GND                                                                                                                                                                                                                      |

| 30                                                                         | XOUT                                                                                           | 0            | Not used.                                                                                                                                                                                                                |

| 31                                                                         | XIN                                                                                            | ı            | Input from crystal clock.                                                                                                                                                                                                |

| 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45 | XFSY<br>SUB<br>SBSY<br>RCK<br>SFSY<br>CDROM<br>Ф8<br>WDCK<br>L/R<br>DGL<br>DGR<br>DF01<br>DF00 | 000-00000000 | Not used.                                                                                                                                                                                                                |

| 46                                                                         | SCK                                                                                            | ı            | This terminal is connected to $\mu COM$ . It is an input terminal that carries the clock signal for data transfers.                                                                                                      |

| 47                                                                         | R/W                                                                                            | I            | This connects with microcomputer and it is an output terminal for switching data transmission mode. it enables to transmit data from SVC to microcomputer when R/M is "L" and from microcomputer to SVC when R/W is "H". |

| 48                                                                         | <u>CS</u>                                                                                      | ı            | This is a chip select terminal for YM7121.                                                                                                                                                                               |

| 49                                                                         | DOUT                                                                                           | 0            | This terminal is the data output terminal connected to $\mu$ COM. When R/W is low, data is transferred from YM7121 to $\mu$ COM, according to the SCK clock input.                                                       |

| Pin No.                                | Symbol                                            | 1/0   | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------|---------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50                                     | WQ                                                | 0     | This terminal is connected to $\mu$ COM. It is a request signal which demands to $\mu$ COM inputting the data transfer (YM7121 to $\mu$ COM).                                                                                                                                                                                                                                                                                                                                                                                 |

| 51                                     | DIN                                               | ı     | This is a data input terminal connected to $\mu$ COM. When R/W is high, the data is transferred from $\mu$ COM to YM7121 according to the SCK clock input.                                                                                                                                                                                                                                                                                                                                                                    |

| 53<br>54                               | DM+<br>DM-                                        | 0 0   | These terminals output the PWM to control the speed of spindle motor. The speed of the motor goes up when DM + is high, and slows down when DM - is high: both terminals can not become high simultaneously.                                                                                                                                                                                                                                                                                                                  |

| 55<br>56<br>60<br>61<br>62<br>63<br>64 | HF<br>TER<br>TRHD<br>TRGL<br>TROF<br>KP –<br>KP + | 00000 | When tracks are being crossed during serches, the amplitude variation of the generated HF signal is sampled at the zero – cross point of the tracking error signal TER and the TROF signal is output. The level variations of this signal turn the servo on and off, greatly facilitaing track acquisition. KP + or KP – is output to conduct tracking, and TRHD is output during tracking to cause generation of the tracking error signal. The TRGL signal is for increasing the tracking gain after tracking is completed. |

| 57<br>58<br>59                         | FEM +<br>FEM –<br>FEOF                            | 000   | The FEM + and FEM - are output as high speed feed signals, and FEOF signal is output for cutting the feed servo during high speed feed.                                                                                                                                                                                                                                                                                                                                                                                       |

| 65                                     | TRBK                                              | l     | TRBK is input to apply tracking brake from outside. TRGL becomes low with high input and inner control signal TBKE becomes high.                                                                                                                                                                                                                                                                                                                                                                                              |

| 66                                     | SVOF                                              | -     | When the signal inputs to SVOF, tracking and feed servo set to OFF. TROF and FEOF become "H" with high input, and TRHD, KP+, KP- become low.                                                                                                                                                                                                                                                                                                                                                                                  |

| 67<br>58<br>59                         | FZC<br>FCS<br>FRF                                 | - 0 - | These terminals are used for controlling the focus servo.  The FCS is for a leading signal of Focusing; the signal, generated when the focus point is achieved, terminate the focusing operation; and FCO flag is dropped internally by FRF signal generated when reflected light is detected.                                                                                                                                                                                                                                |

| 71                                     | īC                                                | I     | YM7121 needs initializing when power supply turn on. IC will be low more than $400\mu s$ since XIN is input clock with VDD standard.                                                                                                                                                                                                                                                                                                                                                                                          |

| 73<br>74<br>75                         | SLVL<br>EFMX<br>EFMX                              | 0 0   | Amplitude limited, mutually anti-phased signals are output from EFMX and EMFX.  Slice level is controlled by these signals and external amplifier. SLVL is output amplitude alteration component of both terminals. When integral circuit is connected to external. YM7121 easily can control slice level.                                                                                                                                                                                                                    |

| 76                                     | EFMI                                              | 1     | This terminal is input EFM signal. (1~2 Vpp)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 78                                     | PCO                                               | 0     | This terminal outputs the phase difference when the polarity of the clock and the EFM pattern changes.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 79                                     | VPLL                                              | 1     | This terminal is input D.C. voltage matched VCO free run frequency. (17.2872 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 80                                     | 1/2 VPLL                                          | 0     | This terminal outputs a half of VPLL input, and capacity for stabilizing is added to this terminal.                                                                                                                                                                                                                                                                                                                                                                                                                           |